存储系统

存储系统

4.1 概述

存储器分类

按存储介质分类

存储介质 实例 半导体存储器 TTL、MOS(易失)

PROM、FLASH(非易失)磁表面存储器 磁盘、磁带(非易失) 磁芯存储器 已淘汰(非易失) 光盘存储器 激光、磁光材料(非易失) - 按存取方式分类

- 存取时间与物理地址无关(随机访问)

- 随机存储器(RAM)

- 只读存储器(ROM)

- 存取时间与物理地址有关(串行访问)

- 顺序存取存储器:磁带

- 直接存取存储器:磁盘

- 存取时间与物理地址无关(随机访问)

- 在计算机中的作用分类

- 主存储器

- RAM

- 静态RAM:以触发器原理寄存信息

- 动态RAM:以电容充放电原理寄存信息

- ROM

- MPROM、PROM、EPROM、EEPROM、NOR Flash

- RAM

- 闪存(Flash Memory)

- 高速缓冲存储器(Cache)

- 辅助存储器

- 磁盘、磁带、光盘、NAND Flash

- 主存储器

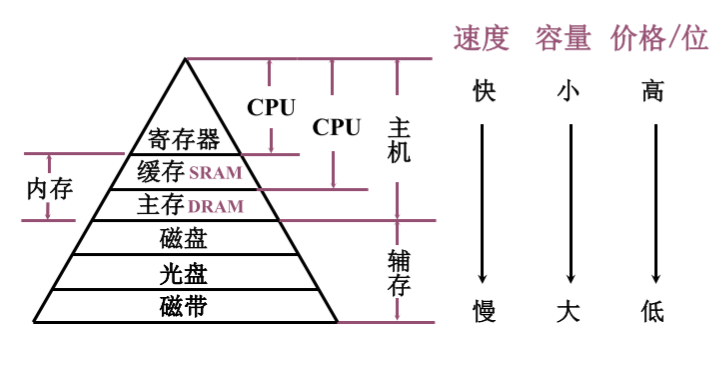

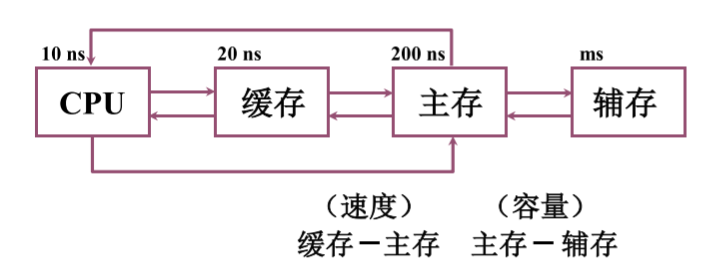

存储器的层次结构

4.2 主存储器

概述

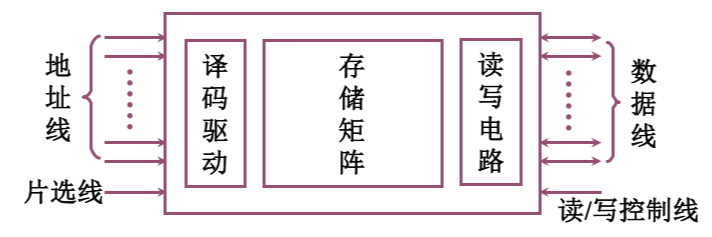

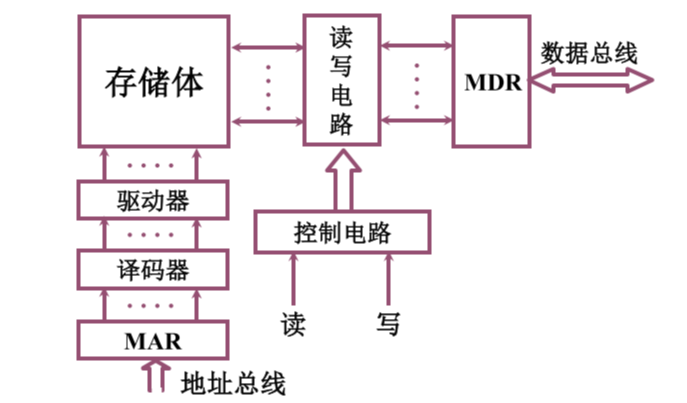

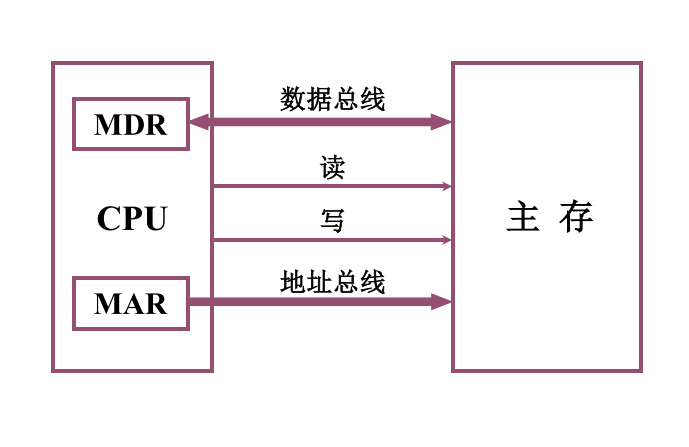

- 基本组成

- 主存和CPU的联系

- 存储单元地址的分配

- 按字寻址(存储字长通常取8的倍数)

- 可由高位字节表示,也可由低位字节表示

- 按字节寻址

- 按字寻址(存储字长通常取8的倍数)

- 技术指标

- 存储容量:存储单元个数x存储字长

- 存储速度

- 存取时间:存储器的访问时间(读出时间、写入时间)

- 存取周期:连续两次独立的存储器操作(读或写)所需的最小间隔时间

- 存储器的带宽:单位时间内存储器存取的信息量

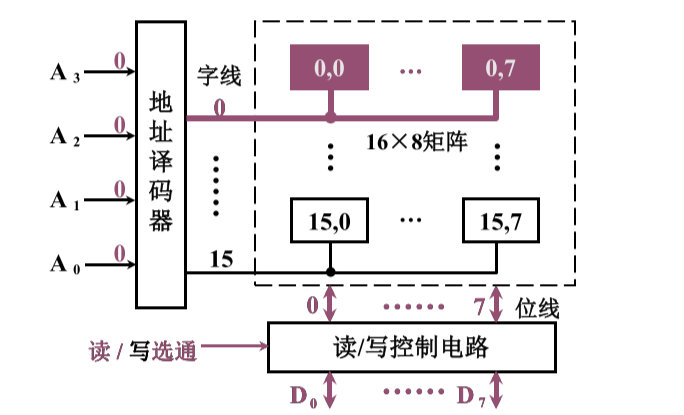

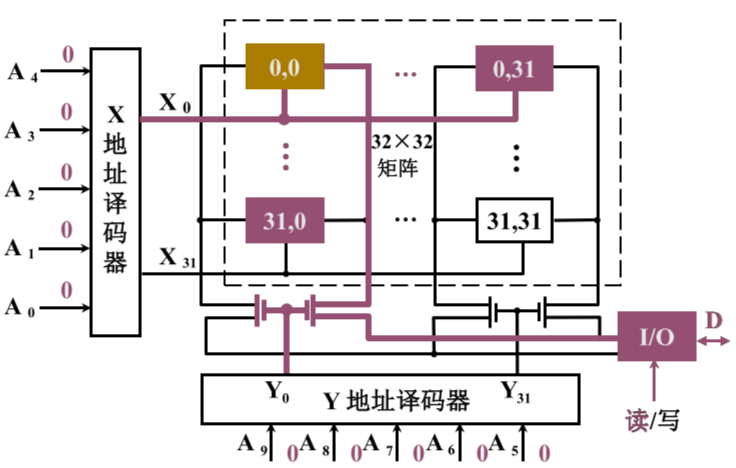

半导体存储芯片

随机存取存储器(RAM)

静态RAM

动态RAM

对比

DRAM(主存) SRAM(缓存) 存储原理 电容 触发器 集成度 高 低 芯片引脚 少 多 功耗 小 大 价格 低 高 速度 慢 快 刷新 需要 不需要

只读存储器(ROM)

- 掩膜ROM

- 行列选择线交叉处有MOS管为“1”

- 行列选择线交叉处无MOS管为“0”

- PROM(一次性编程)

- 熔丝断为“0”

- 熔丝未断为“1”

- EPROM(可擦除可编程)

- 擦除:用紫外线照射,驱散浮动栅

- EEPROM(电可擦除编程)

- FLash Memory(快擦型存储器)

存储器与CPU的连接

- 存储器容量的扩展

- 位扩展:增加存储字长

- 字扩展:增加存储字的数量

- 字、位扩展

- :star:存储器与CPU的连接

- 地址线的连接

- 总是将CPU地址线的低位与存储芯片的地址线相连

- 数据线的连接

- 数据线必须相等,否则对存储芯片进行扩位

- 读/写线的连接

- 片选线的连接

- CPU的访存控制信号$\overline{MREQ}$低电平有效(该信号有效时才能选择存储芯片)

- 合理选用芯片

- ROM:存放系统程序、标准子程序和各类常数等

- RAM:为用户编程而设置的

- 其他:时序、负载……

- 地址线的连接

- 74138芯片

- 使能端:一个高使能,两个低使能

- 选中输出低电平

- 解题流程

- 写出对应的二进制地址码

- 确定芯片的数量及类型

- 分配地址线

- 确定片选信号

- 画出连接图

存储器的校验

奇偶校验码

- 偶校验:$P_e=b_{n-1}\bigoplus b_{n-2}\bigoplus …\bigoplus b_1\bigoplus b_0$

- 奇校验:$P_o=b_{n-1}\bigoplus b_{n-2}\bigoplus …\bigoplus b_1\bigoplus b_0\bigoplus 1$

汉明校验码

- 汉明距离

- 两个码字对应位置不同字符的个数

- 最小汉明距离

- 在一个码组集合中,任意两个编码之间汉明距离的最小值

- $L-1=D+C(D>=C)$

- L为编码的最小汉明距离;

D为检测错误的位数;

C为纠正错误的位数

- L为编码的最小汉明距离;

- 汉明码:具有一位纠错能力的编码

- $2^k\geq n+k+1$(k为需要增添的检测位)

- k个检测位分别插入到$2^i$的位置

- 原因:这些检测位的取值担任所在检测小组中的奇偶校验任务

提高访存速度的措施

- 采用高速器件

- 采用层次结构Cache——主存

- 调整主存结构

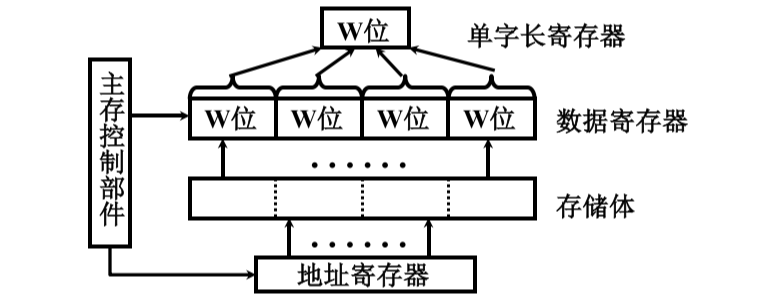

(1)单体多字系统

- 一个周期可读取4xW位的指令或数据

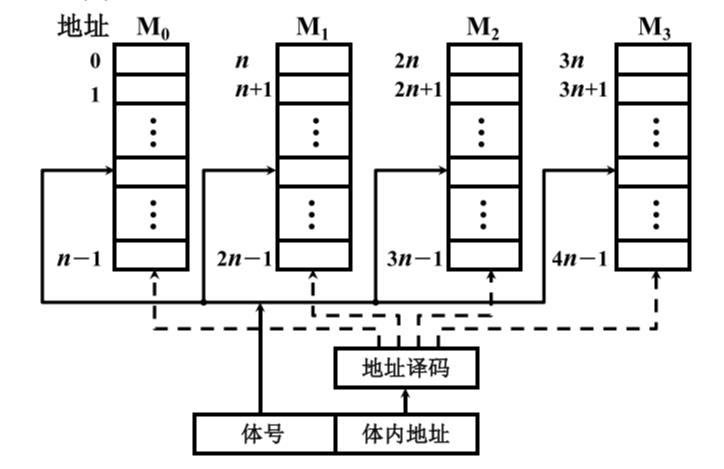

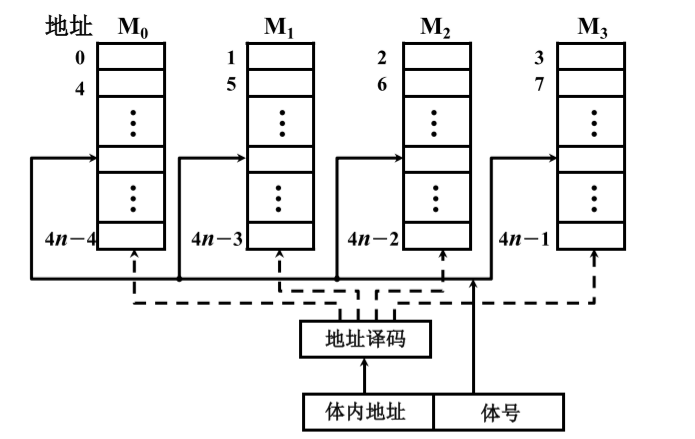

(2)多体并行系统

- 采用多体模块组成的存储器

- 每个模块有独立的MAR、MDR、地址译码、驱动电路和读/写电路

- 高位交叉(顺序存储)

- 各存储体连续编址

- 有利于存储器的扩充

- 低位交叉(交叉存储)

- 各存储体轮流编址

- 有利于增加存储器的带宽

- 读取时间

- 高位交叉:$t=nT$

- 低位交叉:$t=T+(n-1)\tau$ 其中,$T$为存取周期,$\tau$为总线传输周期

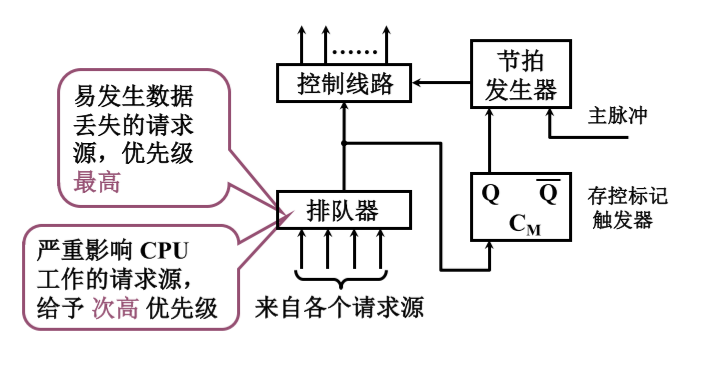

- 存储器控制部件(存控)

(3)高性能存储芯片

- SDRAM(同步DRAM)

- 在系统时钟的控制下进行读出和写入

- CPU无需等待

- RDRAM

- 主要解决存储器带宽的问题

- 带Cache的DRAM(CDRAM)

- 在DRAM的芯片内集成了一个由SRAM组成的Cache,有利于猝发式读取

4.3 高速缓冲存储器

概述

- 问题

- 避免CPU与I/O设备争抢访存,导致CPU“空等”

- CPU和主存的速度差异

程序访问的局部性原理

- 时间局部性:程序马上将要用到的信息很可能就是现在正在使用的信息(多次调用)

- 空间局部性:程序马上将要用到的信息很可能与现在正在使用的信息在存储空间上是相邻的(数据指令连续存放)

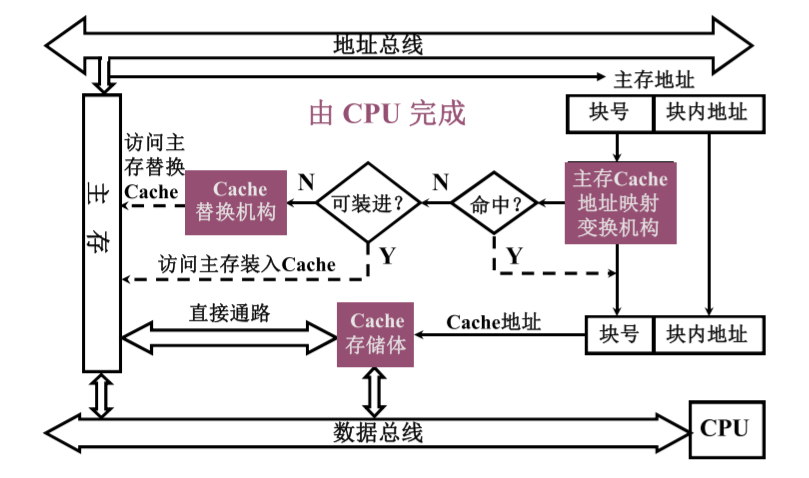

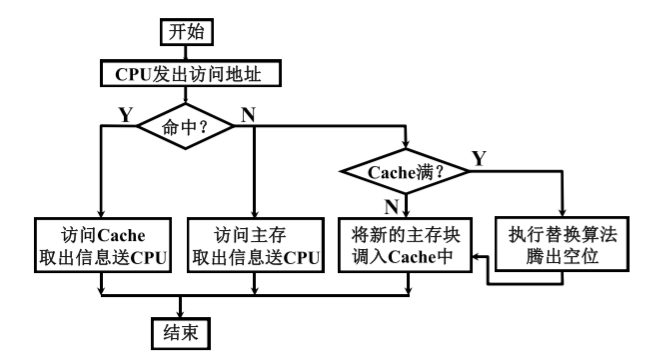

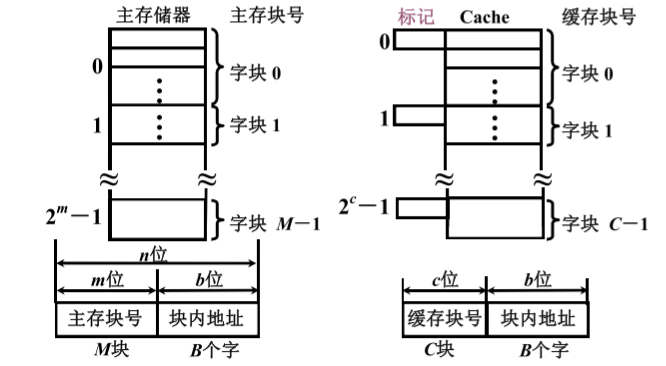

Cache的工作原理

- 主存和缓存的编址

- 按块存储,块大小相同,M » C

- 命中与未命中

- CPU访问Cache命中

- 主存块已调入缓存(主存块与缓存块已建立了对应关系)

- 标记:缓存用来表示当前存放的是哪一个主存块

- CPU访问Cache未命中

- 主存块未调入缓存

- CPU访问Cache命中

- Cache的命中率

- $h=\frac{N_c}{N_c+N_m}$

- 与Cache的容量和块长有关

- Cache的平均访存时间(同时访问主存和缓存)

- $t=ht_c+(1-h)t_m$

- Cache-主存系统的效率

- $e=\frac{t_c}{ht_c+(1-h)t_m}\times100\%$

Cache的基本结构

Cache的读写操作

Cache的改进

- 增加Cache的级数

- 两级缓存:片内缓存和片外缓存

- 统一缓存和分立缓存

- 统一缓存:指令数据存放于同一缓存

- 分立缓存:指令数据分别存放于不同的缓存

- 影响因素:与主存结构有关、与指令执行的控制方式有关(超前控制、流水线控制)

Cache-主存的地址映射

| 映射方式 | 解释 | 特点 |

|---|---|---|

| 直接映射 | 主存中每一块只能放置到Cache中唯一的一个位置 | 空间利用率最低,冲突概率最高,实现最简单 |

| 全相联映射 | 主存中的任一块可以被放置到Cache中的任意一个位置 | 空间利用率最高,冲突概率最低,实现最复杂 |

| 组相联映射 | 主存中的每一块可以被放置到Cache中唯一的一个组中的任何一个位置 | 是直接映射和全相联映射的一种折中 |

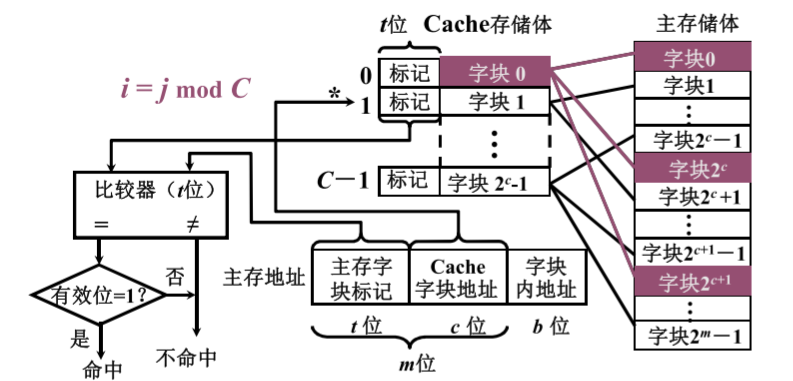

直接映射

- 标记$t=m-c$

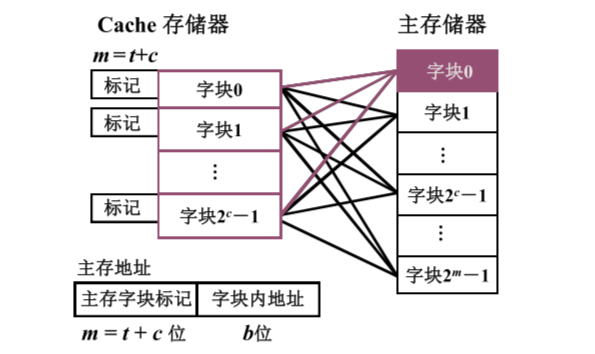

全相联映射

- 标记$m=t+c$

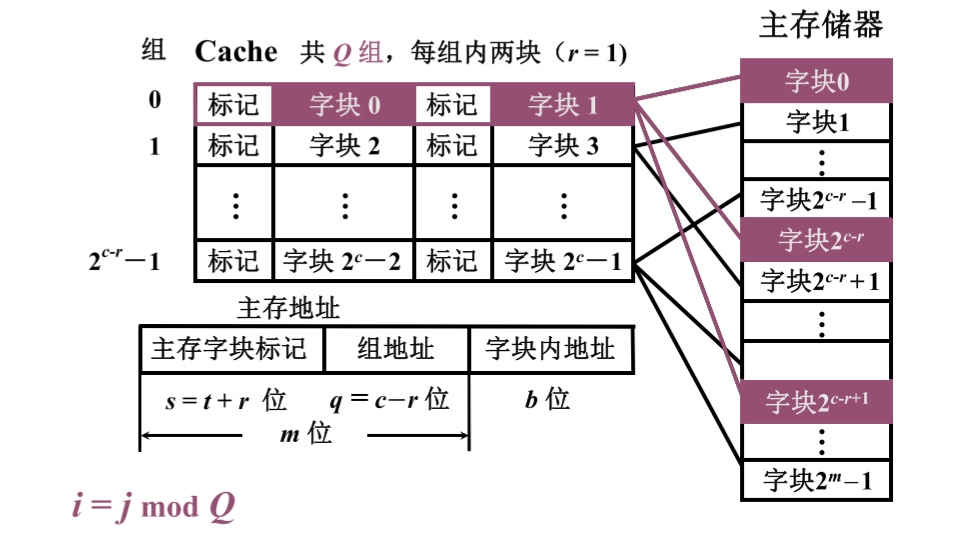

组相联映射

- 标记$s=t+r$

- n路组相联:每组有n个块,n称为相联度

- 相联度越高,Cache的空间利用率就越高,块冲突概率就越低,失效率也就越低

- 大多数计算机的Cache:$n\leq4$

查找方法

替换算法

- 直接映射

- 只有一个块可替代

- 全相联和组相联映射

- 随机法

- 先进先出法FIFO

- 最近最少使用法LRU

- 对于容量足够大的Cache,LRU和随机法的命中率差别不大,而且不低,实现简单,被广泛采用

改进Cache性能

- 平均访存时间

- 不能同时访问主存和缓存(默认):$t=t_c+(1-h)t_m$(命中时间+失效率x失效开销)

- 同时访问主存和缓存:$t=ht_c+(1-h)t_m$ 1. 降低失效率

- 增加块大小,提高相联度

- 减少失效开销

- 多级Cache,写缓存,请求字优先处理

- 减少Cache命中时间

- 容量小且结构简单的Cache

- 增加块大小,提高相联度

4.4 虚拟存储器

概述

- 主存、辅存在OS和硬件的管理之下,提供更大的存储空间

基本原理

虚存管理方式

- 页式管理

- 把主存和外存均划分成等长的页面

- 段式管理

- 把空间划分成可变长的块(段),段与程序相对应

- 段页式管理

页式虚拟存储器

略

This post is licensed under CC BY 4.0 by the author.