指令系统

指令系统

6.1 机器指令

指令的一般格式

- 操作码 + 地址码

- 操作码

- 可分为定长和变长

- 变长的使用扩展操作码技术

- 地址码

- 四地址、三地址、二地址、一地址、零地址

- 操作码

指令字长

- 取决于操作码的长度、操作数地址的长度、操作数地址的个数

- 指令字长固定

- 指令字长 = 存储字长

- 指令字长可变

- 按字节的倍数变化

6.2 操作数类型和操作种类

操作数类型

- 地址、数字、字符、逻辑数

数据在存储器中的存放方式

- 字节次序

- 大端法:高位字节存放在低位地址

- 小端法:低位字节存放在低位地址

- 存储器中的数据存放

- 边界对准、边界未对准

操作类型

- 数据传送

- 算数逻辑操作

- 移位操作

- 转移

- 无条件转移 JMP

- 条件转移

- 调用和转移

- 陷阱/陷阱指令

- 意外事故的中断

- 一般不提供给用户直接使用

- 在出现事故时,由CPU自动产生并执行(隐指令)

- 设置供用户使用的陷阱指令

- 输入输出

- IO单独编址

6.3 寻址方式

指令寻址

- 顺序

- PC++

- 跳跃

- 由转移指令指出

数据寻址

操作码 寻址特征 形式地址A 形式地址A:指令字中的地址

有效地址EA:操作数的真实地址

- 立即寻址

- 直接寻址

- EA = A

- 执行阶段访存一次

- A 的位数决定了该指令操作数的寻址范围

- 隐含寻址

- 操作数地址隐含在操作码中

- 指令字中少了一个地址字段,可缩短指令字长

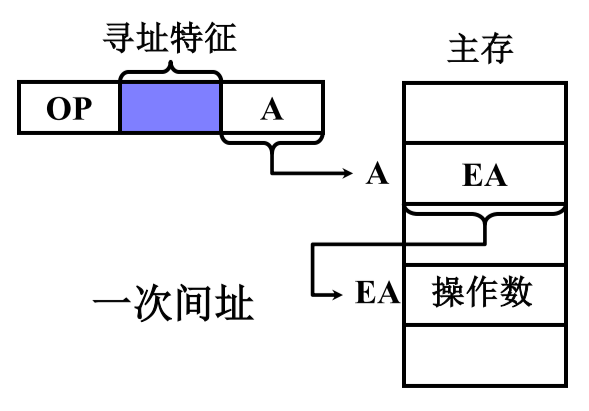

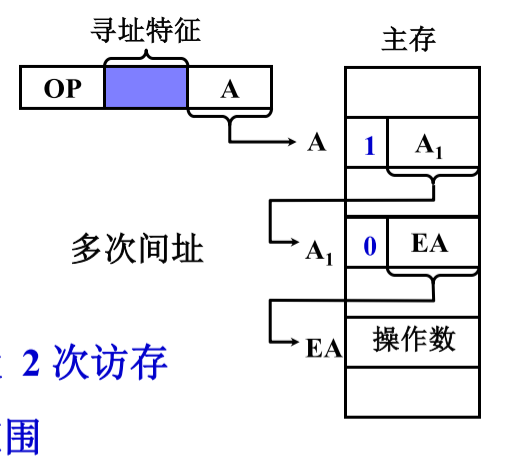

- 间接寻址

- 寄存器寻址

- 执行阶段不访存,只访问寄存器,执行速度快

- 寄存器个数有限,可缩短指令字长

- 寄存器间接寻址

- bala

- 基址寻址

- 采用专用寄存器作基址寄存器

- EA = (BR) + A

BR为基址寄存器 - 在程序的执行过程中BR内容不变,形式地址A可变

- EA = (BR) + A

- 采用通用寄存器作基址寄存器

- EA = (R0) + A

- 在程序的执行过程中R0内容不变,形式地址A可变

- 采用专用寄存器作基址寄存器

- 变址寻址

- EA = (IX) + A

IA为变址寄存器(专用) - 在程序的执行过程中IX内容可变,形式地址A不变

- 便于处理数组问题

- EA = (IX) + A

- 相对寻址

- EA = (PC) + A

- A是相对于当前指令的位移量(可正可负,补码)

- 便于编写浮动程序

- 堆栈寻址

- 栈顶地址由SP指出

6.4 指令格式

设计指令格式应考虑的各种因素

- 指令系统的兼容性(向上兼容)

- 操作类型、数据类型、指令格式、寻址方式、寄存器个数

常见的指令格式

RISC:精简指令系统计算机

CISC:复杂指令系统计算机

- Intel 8086指令格式(CISC)

- 指令字长:1~6个字节

- 地址格式:零地址、一地址、二地址

- MIPS指令格式(RISC)

- 有且只有3种指令格式:R型指令、I型指令、J型指令

- ARM指令系统(RISC)

- 32位的ARM指令集和16位的Thumb指令集,并能够无缝切换

RISC和CISC的比较

RISC CISC 只实现使用频率较高的一些简单指令

复杂指令的功能由简单指令来组合系统指令复杂庞大,各种指令使用频率相差大 指令长度固定、指令格式种类少、寻址方式少 指令长度不固定、指令格式种类多、寻址方式多 只有LOAD/STORE指令访存 访存指令不受限制 CPU中有多个通用寄存器 CPU中设有专用寄存器 采用流水技术、一个时钟周期内完成一条指令 大多数指令需要多个时钟周期执行完毕 采用组合逻辑实现控制器 次啊用微程序控制器 采用优化的编译程序 难以用优化编译生成高效的目标代码

This post is licensed under CC BY 4.0 by the author.